# HIGH-POWER, WIDE VOLTAGE RANGE, QUAD-PORT ETHERNET POWER SOURCING EQUIPMENT MANAGER

# **FEATURES**

- Quad-Port Power Management With Integrated Switches and Sense Resistors

- High Power PoE up to 25 W at PD Input **Operating from a 53-V Minimum Input Power** Rail

- Wide Range Single Supply: 21.5 V up to 57 V •

- $I_{CUT} = 615 \text{ mA}, I_{LIM} = 650 \text{ mA Nominal}$ •

- **IEEE 802.3af Compatible**

- Individual Port 15-bit A/D Converters •

- Auto, Semi-Auto and Power Management • Modes

- Controlled Current Ramp Power-Up/Down for **EMI** Reduction

- **Over-Temperature Protection**

- **DC Disconnect Detection, Supports AC** • Disconnect

- High-Speed 400-kHz I<sup>2</sup>C Interface •

- Supports Legacy PD Detection •

- **PowerPAD<sup>™</sup> Package** •

- **Comprehensive Power Management Software** Available for MPS430 Microcontroller

# APPLICATIONS

- Medical/Industrial Applications at 24 V

- **High Power Ethernet Enterprise Switches**

- **SOHO Hubs. Ethernet Hubs**

- **Ethernet High Power Mid-Spans**

- **High Power PSE Injectors**

### DESCRIPTION

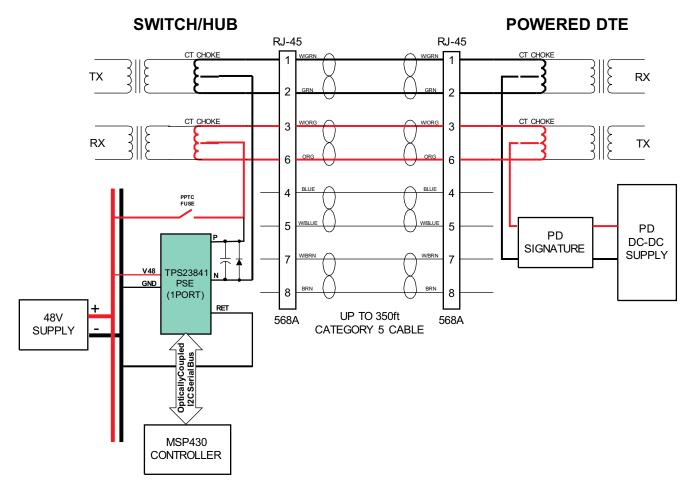

The TPS23841 is a high-power, wide voltage range, quad-port sourcing equipment manager. The TPS23841 can provide up to 570 mA per port over a wide temperature range (-40°C to +125°C). Each port may operate from 21.5 V up to 57 V. The integrated output eliminates two external components per port (MOSFET and sense resistor) and survives 100-V transients. Four individual 15-bit A/D converters are used to measure signature resistance, voltage, current and die temperature, resulting in a simple and robust PSE solution. The TPS23841 comes with a comprehensive software solution to meet the most demanding applications which can serve as a core for all PoE system designs.

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet. PowerPAD is a trademark of Texas Instruments.

54

#### Copyright © 2006, Texas Instruments Incorporated

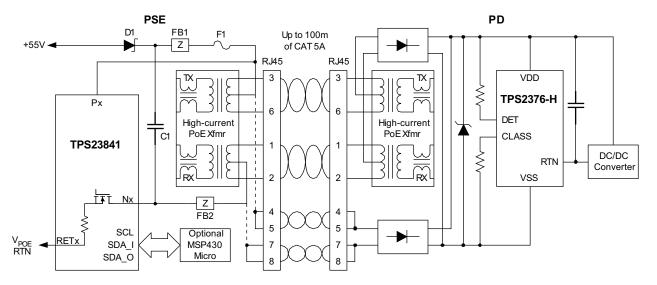

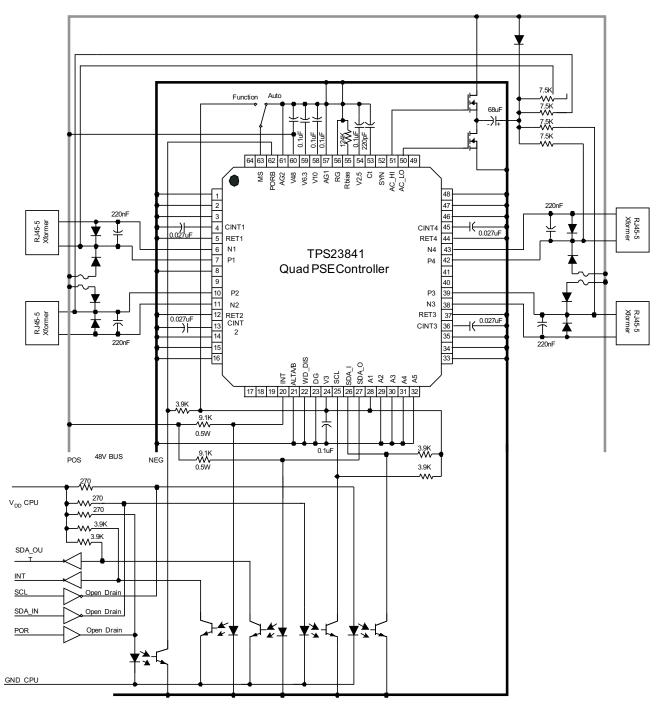

### **TYPICAL APPLICATION**

### **DESCRIPTION (CONTINUED)**

The TPS23841 has three internal supply buses (10 V, 6.3 V and 3.3 V) generated from the 48-V input supply. These supplies are used to bias all internal digital and analog circuitry. Each supply has been brought out separately for proper bypassing to insure high performance. The digital supply (3.3 V) is available for powering external loads up to 2 mA. For more demanding loads it is highly recommended to use external buffers to prevent system degradation. When the TPS23841 is initially powered up an internal Power-on-Reset (POR) circuit resets all registers and sets all ports to the off state to ensure that the device is powered up in a known safe operating state.

The TPS23841 has three modes of operation; auto mode (AM), semi-auto mode (SAM) and power management mode (PMM).

- In auto mode the TPS23841 performs discovery, classification and delivery of power autonomously to a compliant PD without the need of a micro-controller.

- In semi-auto mode the TPS23841 operates in auto mode but users can access the contents of all read status

registers and A/D registers through the I<sup>2</sup>C serial interface. All write control registers are active except for D0

through D3 of port control register 1 (Address 0010) for limited port control. The semi-auto mode allows the

TPS23841 to detect valid PD's without micro-controller intervention but adds a flexibility to perform power

management activities.

- Power management mode (with a micro-controller) allows users additional capabilities of discovering non-compliant (legacy) PDs, performing AC Disconnect and advanced power management system control that are based on real time port voltages and currents. All functions in this mode are programmed and controlled through read/write registers over the I<sup>2</sup>C interface. This allows users complete freedom in detecting and powering devices. A comprehensive software package is available that mates the power of the TPS23841 with the MSP430 micro-controller.

TPS23841 integrated output stage provides port power and low-side control. The internal low-side circuitry is designed with internal current sensing so there are no external resistors required. The output design ensures the power switches operate in the fully enhanced mode for low power dissipation.

The I<sup>2</sup>C interface allows easy application of opto-coupler circuitry to maintain Ethernet port isolation when a ground based micro-controller is required. The TPS23841 five address pins (A1–A5) allow the device to be addressed at one of 31 possible I<sup>2</sup>C addresses. Per-port write registers separately control each port state (discovery, classification, legacy, power up, etc) while the read registers contain status information of the entire process along with parametric values of discovery, classification, and real-time port operating current, voltage and die temperature.

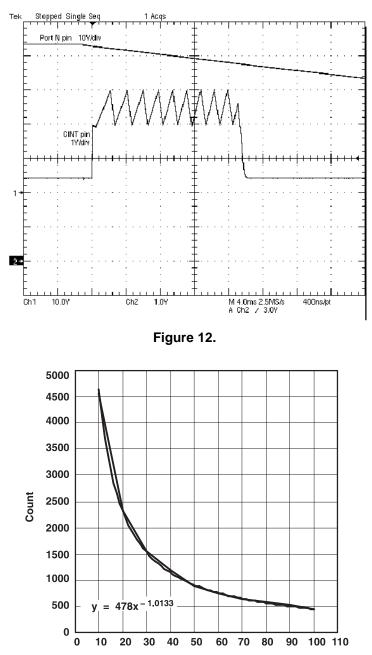

The proprietary 15-bit integrating A/D converter is designed to meet the harsh environment where the PSEPM resides. The converter is set for maximum rejection of power line noise allowing it to make accurate measurements of line currents during discovery, classification and power delivery for reliable power management decisions.

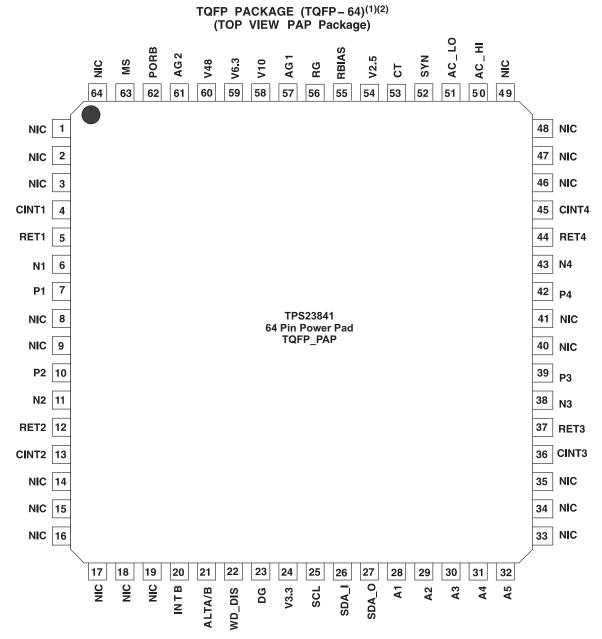

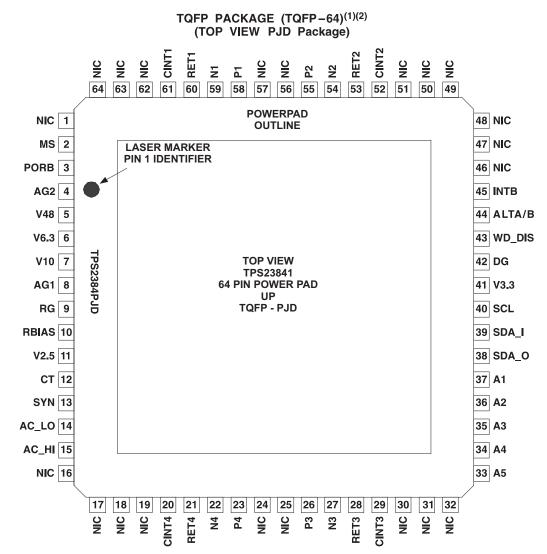

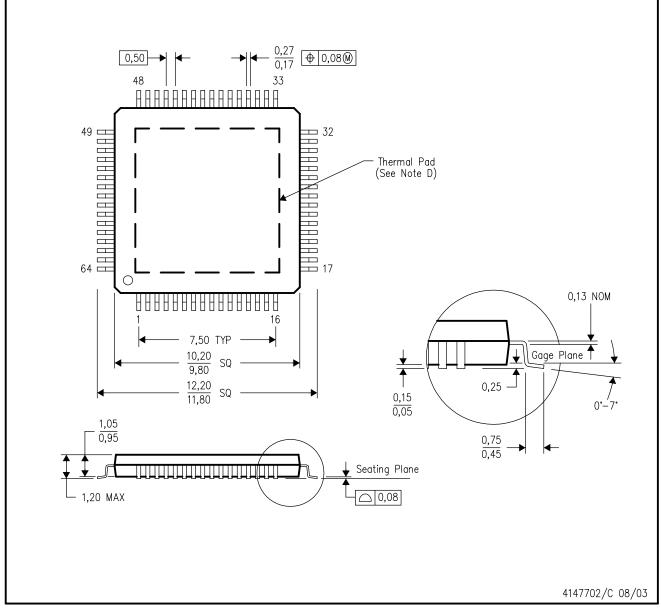

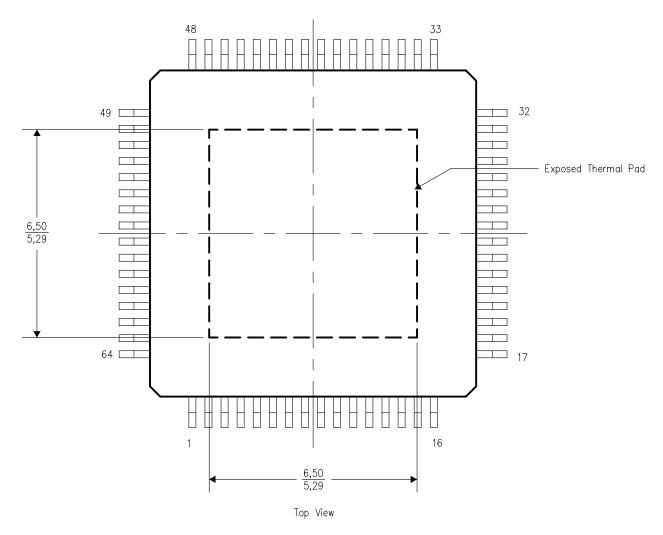

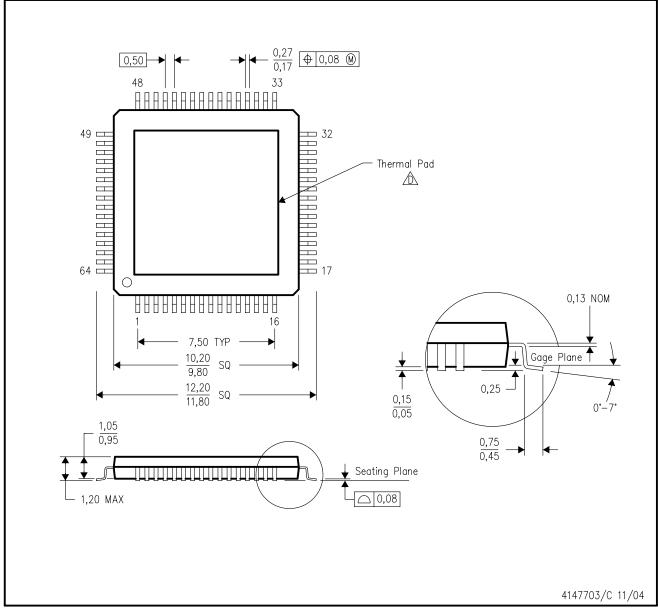

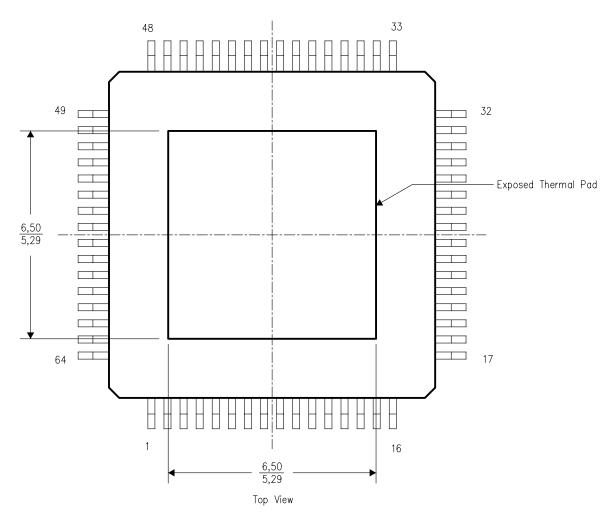

The TPS23841 is available in either 64-pin PowerPAD<sup>™</sup> down (PAP) or 64-pin PowerPAD up (PJD) packages.

| TEMPERATURE RANGE | PACKAGED                       | DEVICES <sup>(1)</sup>         |

|-------------------|--------------------------------|--------------------------------|

| $T_A = T_J$       | TQFP – 64 (PAP) <sup>(2)</sup> | TQFP – 64 (PJD) <sup>(2)</sup> |

| -40°C to 125°C    | TPS23841PAP                    | TPS23841PJD                    |

#### ORDERING INFORMATION

(1) The PAP and PJD packages are available taped and reeled. Add R suffix to device type

(e.g.TPS23841PAPR) to order quantities of 1,000 devices per reel.

(2) PAP = PowerPad down, PJD = PowerPad up.

### **ABSOLUTE MAXIMUM RATINGS**

over operating free-air temperature range (unless otherwise noted) (1)(2)

|                  | PARAMETER                                                                                               | VALUE      | UNIT |

|------------------|---------------------------------------------------------------------------------------------------------|------------|------|

|                  | V10 current sourced                                                                                     | 100        | μA   |

|                  | V3.3 current sourced                                                                                    | 5          | mA   |

|                  | Applied voltage on CINT#, CT, RBIAS                                                                     | -0.5 to 10 |      |

|                  | Applied voltage on SCL, SDA_I, SDA_O, INTB, A1, A2, A3, A4, A5, MS, PORB, WD_DIS, ALT_A/B, AC_LO, AC_HI | -0.5 to 6  | V    |

|                  | Applied voltage on V48, P#, N#                                                                          | -0.5 to 80 |      |

| TJ               | Junction operating temperature                                                                          | -40 to 125 |      |

| T <sub>stg</sub> | Storage temperature55 to 150                                                                            | -55 to 150 | °C   |

| T <sub>sol</sub> | Lead temperature (soldering, 10 sec.)                                                                   | 260        |      |

(1) Stresses beyond those listed under *absolute maximum ratings* may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under *recommended operating conditions* is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

(2) All voltages are with respect to GND. Currents are positive into, negative out of the specified terminal. Consult Packaging Section of the Data book for thermal limitations and considerations of packages.

### DISSIPATION RATINGS<sup>(1)</sup>

| PACKAGE | THERMAL RESISTANCE JUNCTION TO CASE $\theta_{JC}$ | THERMAL RESISTANCE JUNCTION TO AMBIENT $\theta_{\text{JA}}$ |

|---------|---------------------------------------------------|-------------------------------------------------------------|

| PAP     | 0.38°C/W                                          | 21.47°C/W                                                   |

| PJD     | 0.38°C/W                                          | 21.47°C/W                                                   |

(1) Thermal Resistance measured using 2-oz copper trace and copper pad solder following layout recommendation in TI Publication PowerPAD Thermally Enhanced Package Technical Brief SLMA002.

#### **RECOMMENDED OPERATING CONDITIONS**

over operating free-air temperature range (unless otherwise noted)

| PARA            | MIN                    | NOM  | MAX | UNIT |    |

|-----------------|------------------------|------|-----|------|----|

| V <sub>IN</sub> | Input voltage, V48 pin | 21.5 | 48  | 57   | V  |

| TJ              | Junction temperature   | -40  |     | 125  | °C |

# **ELECTRO STATIC DISCHARGE (ESD) PROTECTION**

|                  | MAX | UNIT |

|------------------|-----|------|

| Human body model | 1.5 |      |

| CDM              | 1   | kV   |

| Machine model    | 0.2 |      |

# TPS23841

SLUS745-NOVEMBER 2006

#### **ELECTRICAL CHARACTERISTICS**

V48 = 48 V,  $R_T$  = 124 k $\Omega$ ,  $C_T$  = 220 pF,  $C_{INT}$  = 0.027  $\mu$ F (low leakage), -40°C to 125°C and  $T_A = T_J$  (unless otherwise noted)

| PARAMETER                                         | TEST CONDITIONS                                                      | MIN  | TYP   | MAX  | UNIT            |

|---------------------------------------------------|----------------------------------------------------------------------|------|-------|------|-----------------|

| Power Supply                                      |                                                                      |      |       |      |                 |

| V48 quiescent current                             | Off mode (all ports)                                                 | 4    | 9     | 12   | mA              |

| V48 quiescent current                             | Powered mode (all ports)                                             |      | 10    | 14   | ША              |

| V10, internal analog supply                       | $I_{LOAD} = 0$                                                       | 9.75 | 10.5  | 11.5 | V               |

| V3.3, internal digital supply                     | $I_{LOAD} = 0$ to 3 mA                                               | 3    | 3.3   | 3.7  | v               |

| V3.3 short circuit current                        | V = 0                                                                | 3    |       | 12   | mA              |

| V6.3, internal supply                             | $I_{LOAD} = 0$                                                       | 5    | 6.3   | 7    |                 |

| V2.5, internal reference supply                   | $I_{LOAD} = 0$                                                       | 2.46 | 2.5   | 2.54 |                 |

| V <sub>UVLO_R</sub> , V48 UVLO                    | Input voltage rising                                                 | 16.0 |       | 21.5 | V               |

| V <sub>UVLO_F</sub> , V48 UVLO                    | Input voltage falling                                                | 14   |       | 21   |                 |

| V <sub>HYSUV</sub> , UVLO hysteresis              |                                                                      | 0.2  | 1.0   | 2.0  |                 |

| Internal POR time out(I <sup>2</sup> C)           | After all supplies are good I <sup>2</sup> C activity is valid       |      | 8     |      | <u>.</u>        |

| Internal POR time out (Port)                      | After all supplies are good Port active to I <sup>2</sup> C commands |      | 66000 |      | Clock<br>Pulses |

| Port Discovery                                    |                                                                      |      |       |      |                 |

| Port off #P to #N input resistance                |                                                                      | 400  | 600   |      | kΩ              |

| Discovery open circuit voltage                    |                                                                      |      | 22    | 30   |                 |

| Discovery 1 voltage loop control                  | 70 μA < I <sub>PORT</sub> < 3 mA                                     | 2.8  | 4.4   |      | V               |

| Discovery 2 voltage loop control                  | 70 μA < I <sub>PORT</sub> < 3 mA                                     |      | 8.8   | 10   |                 |

| Discovery current limit                           | P = N = 48 V                                                         | 3    | 4     | 5    | mA              |

| Auto-mode discovery resistance acceptance Band    |                                                                      | 19   |       | 26.5 |                 |

| Auto-mode discovery resistance low end rejection  |                                                                      | 0    |       | 15   | kΩ              |

| Auto-mode discovery resistance high end rejection |                                                                      | 33   |       |      |                 |

| Discovery1,2 A/D conversion scale factor          | 100 μA < I <sub>PORT</sub> < 3 mA                                    | 5.30 | 6.10  | 6.75 | count/µA        |

| Discovery1,2 A/D conversion time                  | I <sub>PORT</sub> = 120 μA                                           |      |       |      | ms              |

| Port Classification                               | -                                                                    |      |       |      |                 |

| Classification voltage loop control               | 100 μA < I <sub>PORT</sub> < 50 mA                                   | 15   | 17.5  | 20   | V               |

| Classification current limit                      | P = N = 48 V                                                         | 50   | 60    | 100  |                 |

| Class 0 to 1 detection threshold                  |                                                                      | 5.5  | 6.5   | 7.5  |                 |

| Class 1 to 2 detection threshold                  |                                                                      | 13   | 14.5  | 16   |                 |

| Class 2 to 3 detection threshold                  |                                                                      | 21   | 23    | 25   | mA              |

| Class 3 to 4 detection threshold                  |                                                                      | 31   | 33    | 35   |                 |

| Class 4 to 0 detection threshold                  |                                                                      | 45   | 48    | 51   |                 |

| Classification A/D conversion scale factor        |                                                                      | 375  | 424   | 475  | Count/m<br>A    |

| Classification A/D conversion time                | I <sub>PORT</sub> = 50 mA                                            |      | 18    | 22   | ms              |

### **ELECTRICAL CHARACTERISTICS (continued)**

V48 = 48 V,  $R_T$  = 124 k $\Omega$ ,  $C_T$  = 220 pF,  $C_{INT}$  = 0.027  $\mu$ F (low leakage), -40°C to 125°C and  $T_A = T_J$  (unless otherwise noted)

|                                        | PARAMETER                                  | TEST CONDITIONS                                                       | MIN    | TYP      | MAX  | UNIT         |

|----------------------------------------|--------------------------------------------|-----------------------------------------------------------------------|--------|----------|------|--------------|

| Port Le                                | egacy Detection                            |                                                                       | -      |          |      |              |

|                                        | Legacy current limit                       | P = N = 48 V                                                          | 2.6    | 3.5      | 4.3  | mA           |

|                                        | Legacy voltage A/D conversion scale factor | 100 mV < V <sub>PORT</sub> < 17.5 V                                   | 1365   | 1400     | 1445 | Count/V      |

|                                        | Legacy A/D conversion time                 | 0 V < V <sub>PORT</sub> < 15 V                                        |        | 18       | 22   | ms           |

| Port Po                                | owered Mode                                |                                                                       |        |          |      |              |

|                                        | Port on resistance                         | 20 mA < I <sub>PORT</sub> < 300 mA                                    |        | 1.3      | 1.8  | Ω            |

| I <sub>CUT</sub>                       | Over current threshold                     | $R_{BIAS} = 124 \text{ k}\Omega, C_T = 220 \text{ pF},$               | 570    | 615      | 665  |              |

| I <sub>LIM</sub>                       | Output current limit                       |                                                                       | 600    | 650      | 700  |              |

| I <sub>LIM</sub> -<br>I <sub>CUT</sub> | Threshold delta                            |                                                                       | 10     |          | 70   | mA           |

|                                        | Disconnect timer current threshold         | $R_{BIAS} = 124 \text{ k}\Omega, C_T = 220 \text{ pF}$                |        | 7.5      | 10   |              |

| T <sub>MPDO</sub>                      | Disconnect detection time                  | $I_{LOAD}$ < current threshold, $R_{BIAS}$ = 124 kΩ, $C_{T}$ = 220 pF | 300    |          | 400  | ms           |

|                                        | Port output UV                             |                                                                       | 42.0   | 42.7     | 44.0 | V            |

|                                        | Port output OV                             |                                                                       | 54     | 55       | 56   | v            |

| T <sub>OVLD</sub>                      | Over current time out                      | $R_{BIAS} = 124 \text{ k}\Omega, C_T = 220 \text{ pF}$                | 50     |          | 75   |              |

| T <sub>LIM</sub>                       | Short circuit time out                     | RBIAS = 124 k., CT = 220 pF                                           | 50     |          | 75   | ms           |

|                                        | Turnoff delay from UV/OV faults            | RBIAS = 124 k., CT = 220 pF, After port enabled and ramped up         |        | 3        |      | 110          |

|                                        | Port current A/D conversion scale factor   | 20 mA < I <sub>PORT</sub> < 56 V                                      | 31     | 36.41    | 40   | Count/m<br>A |

|                                        | Port current A/D conversion time           | I <sub>PORT</sub> < 300 mA                                            |        | 18       | 22   | ms           |

|                                        | Port voltage A/D conversion scale factor   | 45 V < V <sub>PORT</sub> < 56 V                                       | 335    | 353      | 370  | Count/V      |

|                                        | Port voltage A/D conversion time           |                                                                       |        | 18       | 22   | ms           |

|                                        | Port temperature A/D conversion            |                                                                       | (17500 | - counts | )/16 | °C           |

| Port Di                                | isable Mode                                |                                                                       |        |          |      |              |

|                                        | Port N voltage                             | P = 48 V                                                              | 47     |          |      | V            |

| AC LO                                  | and AC HI Specification                    |                                                                       | ·      |          |      |              |

|                                        | AC_LO, AC_HI – low output voltage          |                                                                       | 0      |          | 0.5  |              |

|                                        | AC_LO – high output voltage                |                                                                       | 3.0    |          | 5.0  | V            |

|                                        | AC_HI – high output voltage                |                                                                       | 5.0    |          | 7.0  |              |

# **ELECTRICAL CHARACTERISTICS (continued)**

$V48 = 48 \text{ V}, \text{ } \text{R}_{\text{T}} = 124 \text{ } \text{k}\Omega, \text{ } \text{C}_{\text{T}} = 220 \text{ } \text{pF}, \text{ } \text{C}_{\text{INT}} = 0.027 \text{ } \mu\text{F} \text{ (low leakage)}, -40^{\circ}\text{C} \text{ to } 125^{\circ}\text{C} \text{ and } \text{T}_{\text{A}} = \text{T}_{\text{J}} \text{ (unless otherwise noted)}$

| PARAMETER                                                               | TEST CONDITIONS           | MIN   | TYP MAX | UNIT |

|-------------------------------------------------------------------------|---------------------------|-------|---------|------|

| Digital I <sup>2</sup> C DC Specifications                              |                           |       |         |      |

| SCL, SDA_I, A1–A5 ,WD_DIS,<br>ALTA/B, MS, PORB logic input<br>threshold |                           |       | 1.5     | V    |

| SCL, SDA_I input hysteresis                                             |                           |       | 250     | mV   |

| MS, PORB input hysteresis                                               |                           |       | 150     | mv   |

| WD_DIS, ALTA/B, MS, PORB input pulldown resistance                      | Input voltage 0.5 to 3 V  |       | 50      | kΩ   |

| A1-A5 pull-down current                                                 |                           |       | 10      | μA   |

| SDA_O logic high leakage                                                | Drain = 5 V               |       | 100     | nA   |

| SDA_O logic low                                                         | I <sub>SINK</sub> = 10 mA |       | 200     | mV   |

| INTB logic high leakage                                                 | Drain = 6 V               |       | 10      | μA   |

| INTB logic low                                                          | I <sub>SINK</sub> = 10 mA |       | 200     | mV   |

| Digital I <sup>2</sup> C Timing                                         |                           |       |         |      |

| SCL clock frequency                                                     |                           | 0     | 400     | kHz  |

| Pulse duration                                                          | SCL high                  | 0.6   |         |      |

| Pulse duration                                                          | SCL low                   | 1.3   |         |      |

| Rise time, SCL to SDA                                                   |                           |       | 0.300   |      |

| Fall time, SCL to SDA                                                   |                           |       | 0.300   |      |

| Setup time, SDA to SCL                                                  |                           | 0.250 |         |      |

| Hold time, SCL to SDA                                                   |                           | 0.300 | 0.900   | μs   |

| Bus free time between start and stop                                    |                           | 1.3   |         |      |

| Setup time, SCL to start condition                                      |                           | 0.6   |         |      |

| Hold time, start condition to SCL                                       |                           | 0.6   |         |      |

| Setup time, SCL to stop condition                                       |                           | 0.6   |         |      |

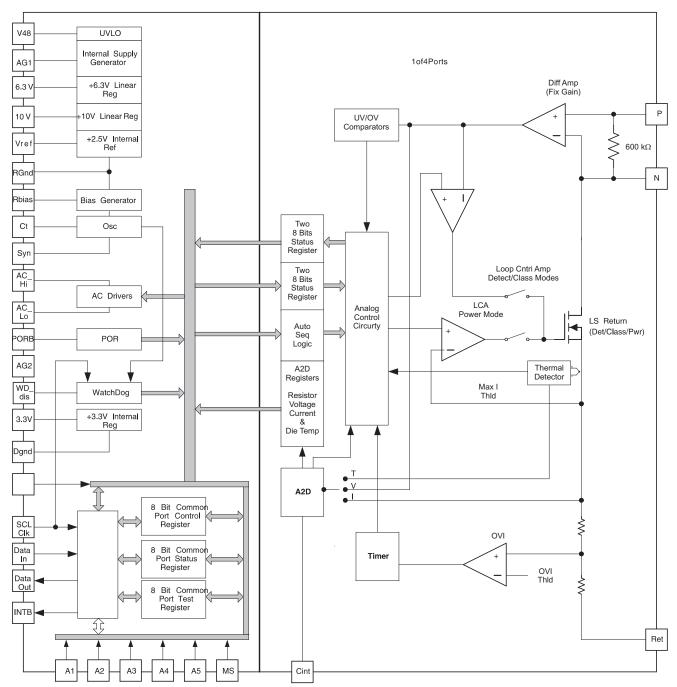

### **TPS23841 SINGLE PORT BLOCK DIAGRAM**

TPS23841 SLUS745-NOVEMBER 2006

#### **TERMINAL FUNCTIONS**

| TERMINAL |         |      |     |                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |

|----------|---------|------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

|          | N       | 0.   | I/O | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |

| NAME     | PAP     | PJD  |     |                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |

| POWER    | AND GRO | UND  |     |                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |

| V48      | 60      | 5    | I   | 48-V input to the device. This supply can have a range of 22 V to 57 V. This pin should be decoupled with a 0.1- $\mu$ F capacitor from V48 to AG1 placed as close to the device as possible.                                                                                                                                                                                 |  |  |  |  |

| V10      | 58      | 7    | 0   | 10-V analog supply. The 10-V reference is generated internally and connects to the main internal analog power bus. A $0.1-\mu F$ de-coupling capacitor should terminate as close to this node and the AG1 pin as possible. Do not use for an external supply.                                                                                                                 |  |  |  |  |

| V6.3     | 59      | 6    | 0   | 6.3-V analog supply. A 0.1- $\mu$ F de-coupling capacitor should terminate as close to this pin and the AG1 pin as possible. Do not use for an external supply.                                                                                                                                                                                                               |  |  |  |  |

| V3.3     | 24      | 41   | 0   | 3.3-V logic supply. The 3.3-V supply is generated internally and connects to the internal logic power bus. A $0.1$ - $\mu$ iF de-coupling capacitor should terminate as close to this node and the DG pin as possible. This output can be used as a low current supply to external logic.                                                                                     |  |  |  |  |

| V2.5     | 54      | 11   | 0   | 2.5-V reference supply. The V2.5 is generated internally and connects to the internal reference power bus. This pin should not be tied to any external supplies. A $0.1-\mu$ F de-coupling capacitor should terminate as close to this node and the RG pin as possible. Do not use for an external supply.                                                                    |  |  |  |  |

| AG1      | 57      | 8    | GND | Analog ground 1. This is the analog ground of the V6.3, V10 and V48 power systems. It should be externally tied to the common copper 48-V return plane. This pin should carry the low side of three de-coupling capacitors tied to V48, V10 and V6.3.                                                                                                                         |  |  |  |  |

| AG2      | 61      | 4    | GND | Analog ground 2. This is the analog ground which ties to the substrate and ESD structures of the device. It should be externally tied to the common copper 48-V return plane. AG1 and AG2 must be tied together directly for the best noise immunity.                                                                                                                         |  |  |  |  |

| DG       | 23      | 42   | GND | Digital ground. This pin connects to the internal logic ground bus. It should be externally tied to the common copper 48-V return plane.                                                                                                                                                                                                                                      |  |  |  |  |

| RG       | 56      | 9    | GND | Reference ground. This is a precision sense of the external ground plane. The integration capacitor (CINT) and the biasing resistor (RBIAS pin) should be tied to this ground. This ground should also be used to form a printed wiring board ground guard ring around the active node of the integration capacitor (CINT). It should tie to common copper 48-V return plane. |  |  |  |  |

| PORT AN  |         | GNAL |     |                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |

| P1       | 7       | 58   | I   |                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |

| P2       | 10      | 55   | I   | Port Positive. 48-V load sense pin. Terminal voltage is monitored and controlled differentially with                                                                                                                                                                                                                                                                          |  |  |  |  |

| P3       | 39      | 26   | 1   | respect to each Port N pin Optionally, if the application warrants, this high side path can be protected with the use of a self resetting poly fuse.                                                                                                                                                                                                                          |  |  |  |  |

| P4       | 42      | 23   | 1   |                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |

| N1       | 6       | 59   | 1   |                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |

| N2       | 11      | 54   | Ι   | Port negative. 48-V load return pin. The low side of the load is switched and protected by internal                                                                                                                                                                                                                                                                           |  |  |  |  |

| N3       | 38      | 27   | I   | circuitry that will limit the current.                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |

| N4       | 43      | 22   | I   |                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |

| RET1     | 5       | 60   | I   |                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |

| RET2     | 12      | 53   | I   |                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |

| RET3     | 37      | 28   | 1   | 48 V return pin                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |

| RET4     | 44      | 21   | I   |                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |

| CINT1    | 4       | 61   | I   |                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |

| CINT2    | 13      | 52   | I   | Integration capacitor. This capacitor is used for the ramp A/D converter signal integration. Connect A 0.027- $\mu$ F capacitor from this pin to RG. To minimize errors use a polycarbonate, poly-polypropylene,                                                                                                                                                              |  |  |  |  |

| CINT3    | 36      | 29   | I   | polystyrene or teflon capacitor type to prevent leakage. Other types of capacitors can be used with                                                                                                                                                                                                                                                                           |  |  |  |  |

| CINT4    | 45      | 20   | I   | increased conversion error.                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |

### **TERMINAL FUNCTIONS (continued)**

| TERMINAL  |         | INAL |     | MINAL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |     | RMINAL      |  | RMINAL |  | RMINAL |  | ERMINAL |  | ERMINAL |  | TERMINAL |  |  |

|-----------|---------|------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-------------|--|--------|--|--------|--|---------|--|---------|--|----------|--|--|

|           | NO.     |      | NO. |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | I/O | DESCRIPTION |  |        |  |        |  |         |  |         |  |          |  |  |

| NAME      | PAP     | PJD  |     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |     |             |  |        |  |        |  |         |  |         |  |          |  |  |

| ANALOG    | SIGNALS | 3    |     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |     |             |  |        |  |        |  |         |  |         |  |          |  |  |

|           |         |      |     | This is a dual-purpose pin. When tied to an external capacitor this pin sets the internal clock. When the CT pin is grounded the SYN pin turns from a output to an input (see SYN pin description)                                                                                                                                                                                                                                                                                                                                                                                         |     |             |  |        |  |        |  |         |  |         |  |          |  |  |

| СТ        | 53      | 12   | I   | The timing capacitor and the resistor on the RBIAS pin sets the internal clock frequency of the device. This internal clock is used for the internal state machine, integrating A/D counters, POR time out, faults and delay timers of each port. Using a 220-pF capacitor for CT and a 124-k $\Omega$ resistor for RBIAS sets the internal clock to 245 kHz and ensure IEEE 802.3af compliance along with maximizing the rejection of 60-Hz line frequency noise from A/D measurements.                                                                                                   |     |             |  |        |  |        |  |         |  |         |  |          |  |  |

| RBIAS     | 55      | 10   | 1   | Bias set resistor. This resistor sets all precision bias currents within the chip. This pin will regulate to 1.25V (V2.5/2) when a resistor is connected between RBIAS and RG. This voltage and RBIAS generate a current which is replicated and used throughout the chip. This resistor also works in conjunction with the capacitors on CT and CINT to set internal timing values. The RBIAS resistor should be connected RG. RBIAS is a high impedance input and care needs to be taken to avoid signal injection from the SYN pin or I <sup>2</sup> C signals.                         |     |             |  |        |  |        |  |         |  |         |  |          |  |  |

| SYN       | 52      | 13   | I/O | This is a dual purpose pin. When the CT pin is connected to a timing capacitor this output pin is a 0v to 3.3V pulse of the internal clock which can be used to drive other TPS23841 SYN pins for elimination of a timing capacitor. When the CT pin is grounded this pin becomes an input pin that can be driven from a master TPS23841 or any other clock generator signal.                                                                                                                                                                                                              |     |             |  |        |  |        |  |         |  |         |  |          |  |  |

| AC_LO     | 51      | 14   | 0   | Totem-pole output pin for AC Disconnect excitation.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |     |             |  |        |  |        |  |         |  |         |  |          |  |  |

| AC_HI     | 50      | 15   | 0   | Totem-pole output pin for AC Disconnect excitation.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |     |             |  |        |  |        |  |         |  |         |  |          |  |  |

| DIGITAL S | SIGNALS |      |     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |     |             |  |        |  |        |  |         |  |         |  |          |  |  |

| SCL       | 25      | 40   | I   | Serial clock input pin for the I <sup>2</sup> C interface.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |     |             |  |        |  |        |  |         |  |         |  |          |  |  |

| SDA_I     | 26      | 39   | I   | Serial data input pin for the I <sup>2</sup> C interface. When tied to the SDA_O pin, this connection becomes the standard bi-directional serial data line (SDA)                                                                                                                                                                                                                                                                                                                                                                                                                           |     |             |  |        |  |        |  |         |  |         |  |          |  |  |

| SDA_O     | 27      | 38   | 0   | Serial data open drain output for the I <sup>2</sup> C interface. When tied to the SDA_I pin, this connection becomes the standard bi-directional serial data line (SDA). This is a open drain output that can directly drive opto-coupler.                                                                                                                                                                                                                                                                                                                                                |     |             |  |        |  |        |  |         |  |         |  |          |  |  |

| WD_DIS    | 22      | 43   | I   | The WD_DIS pin disables the watchdog timer function when connected to 3.3 V. The pin has internal 50-k. resistor to digital ground. The watchdog timer monitors the I <sup>2</sup> C clock pin (SCL) and the internal oscillator activity in power management mode and only the internal oscillator activity in auto mode.                                                                                                                                                                                                                                                                 |     |             |  |        |  |        |  |         |  |         |  |          |  |  |

| INTB      | 20      | 45   | 0   | This is an open-drain output that goes low if a fault condition occurs on any of the 4 ports.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |     |             |  |        |  |        |  |         |  |         |  |          |  |  |

| ALTA/B    | 21      | 44   | I   | When this input is set to logic low there is no back-off time after a discovery failure. When this pin set to a logic high there is a back-off time (approximately 2 seconds) before initiating another discovery cycle. This pin has an internal $50$ -k $\Omega$ resistor pull-down to digital ground.                                                                                                                                                                                                                                                                                   |     |             |  |        |  |        |  |         |  |         |  |          |  |  |

| A1        | 28      | 37   | Ι   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |     |             |  |        |  |        |  |         |  |         |  |          |  |  |

| A2        | 29      | 36   | Ι   | Address 1 through 5 These are the I <sup>2</sup> C address select inputs. Select the appropriate binary address                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |     |             |  |        |  |        |  |         |  |         |  |          |  |  |

| A3        | 30      | 35   | Ι   | on these pins by connecting to the chip ground for a logic low or tying to the V3.3 pin for a logic high.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |     |             |  |        |  |        |  |         |  |         |  |          |  |  |

| A4        | 31      | 34   | Ι   | Each address line has an internal current source pull-down to digital ground.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |     |             |  |        |  |        |  |         |  |         |  |          |  |  |

| A5        | 32      | 33   | I   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |     |             |  |        |  |        |  |         |  |         |  |          |  |  |

| MS        | 63      | 2    | I   | The MS pin selects either the auto mode (MS low) or the power management mode, PMM, (MS high). This pin can be held low for controller-less standalone applications. When MS is low and the POR timing cycle is complete the chip will sequentially <i>Discover, Classify and Power on</i> each port. When MS is set high the ports are controlled by register setting via the I <sup>2</sup> C bus. The MS pin has an internal 50-k $\Omega$ resistor pull-down to analog ground.                                                                                                         |     |             |  |        |  |        |  |         |  |         |  |          |  |  |

| PORB      | 62      | 3    | I   | This pin can be used to override the internal POR. When held low, the $l^2C$ interface, all the state machines, and registers are held in reset. When all internal and external supplies are within specification, and this pin is set to a logic high level, the POR delay will begin. The $l^2C$ interface and registers will become active within 70µs of this event and communications to read or preset registers can begin. The reset delay for the remainder of the chip then extinguishes in 1 second. This pin has an internal 50-k $\Omega$ resistor pull-down to analog ground. |     |             |  |        |  |        |  |         |  |         |  |          |  |  |

| TPS23841              |

|-----------------------|

| SLUS745-NOVEMBER 2006 |

**CONNECTION DIAGRAM**

(1) NIC = No internal connection. Pins are floating.

(2) NIC pins can be tied to the ground plane for improved thermal characteristics and to prevent noise injection from unused pins.

(3) NIC pins next to CINT pins should be tied to ground to prevent noise injection into A/D converter.

(1) NIC = No internal connection. Pins are floating.

(2) NIC pins can be tied to the ground plane for improved thermal characteristics and to prevent noise injection from unused pins.

(3) NIC pins next to CINT pins should be tied to ground to prevent noise injection into A/D converter.

# AUTO MODE FUNCTIONAL DESCRIPTION

### Auto Mode

Auto mode (AM, MS = 0) operation is the basic approach for applying power to IEEE compliant PD's. When AM has been selected the TPS23841 automatically performs the following functions:

- Discovery of IEEE 802.3af compliant powered devices (PD's)

- Classification

- Power delivery

- Port over/under voltage detection, (if enabled, see Over/Under Voltage Fault section)

- Port over current detection (570 mA < I<sub>PORT</sub> < 665 mA</li>

- Port maximum current limit (600 mA < I<sub>PORT</sub> < 700 mA)

- DC Disconnect (5 mA < I<sub>PORT</sub> < 10 mA)</li>

- Thermal shutdown protection (TSD), (T<sub>J</sub> > 150°C)

- Internal oscillator watchdog

In AM the contents of all read registers are available via the I<sup>2</sup>C interface. In addition all control registers except for the function bits can be written. This supports a semi-auto mode where the TPS23841 auto detects compliant PD's while a host can access the A/D registers and class information and then implement power management (including turning a port off, responding to faults, etc).

The write registers that are still active in AM are:

- All ports disable Common Control register 0001b

- Over/Under Voltage Faults Common Control register 0001b

- Software reset Common Control register 0001b

- Disconnect disable Port Control 1 register 0010b

- Discovery fault disable Port Control 1 register 0010b

- Port enable Port Control 2 register 0011b

For alternative B, semi-auto mode implementations which will manipulate the all ports disable or Port Enable bits, please contact the factory for additional application information.

#### **Auto Mode Functional Description**

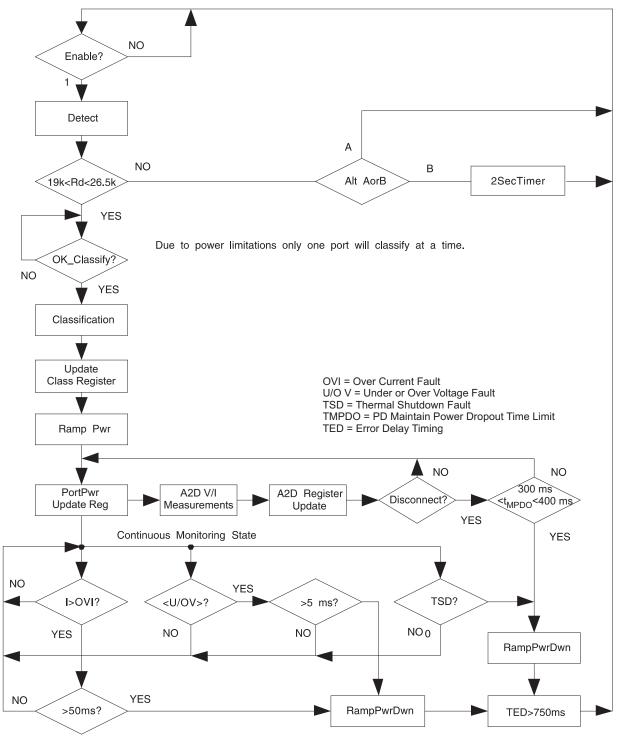

Figure 1. The Basic Flow for Auto Mode

#### **AM Discovery**

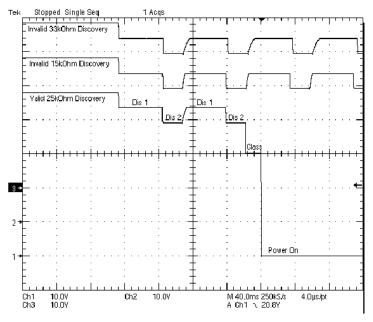

The TPS23841 uses a four-point measurement technique using two low level probe signals (typically 4.4 V and 8.8V) during the discovery process to determine whether a valid PD is present. The use of a multipoint detection method for the PD resistor measurement allows accurate detection even when series steering diodes are present. The low level probe voltages also prevent damage to non-802.3 devices. When a valid PD has been detected the TPS23841 moves to classification. If a valid PD has not been detected the TPS23841 continues to cycle through the discovery process. The waveform in Figure 2 shows typical N-pin waveforms for the discovery of a valid PD and the failure to discovery due to a discovery resistor of 15 k $\Omega$  and 33k $\Omega$ .

Figure 2.

#### **AM Classification**

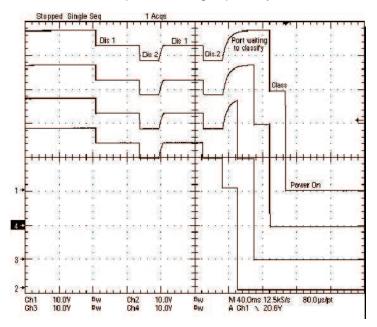

After a successful discovery of a valid PD the TPS23841 enters the classification function that identifies the power level based on the PD's current signature. The classification current level is measured at a reduced terminal voltage of 17.5V. During classification the power dissipation can be at its highest; therefore, to prevent over temperature shutdown in automode only one port classifies at a time. When multiple ports successfully discover and proceed to classification at the same time the auto sequencer processes each request separately allowing only one port to enter classification. Figure 3 shows all 4 ports successfully detecting a valid PD at the same time and than the classification of each port occurring separately.

Figure 3.

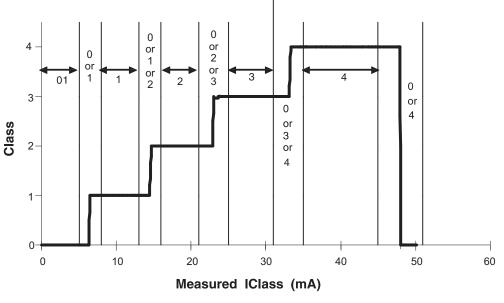

Upon completion of classification the port classification register is updated. In AM mode this information is not used but for semi-auto mode the class information can be used for power management. Figure 4 shows actual class currents and the class assignment which were stored in the register. These assignments are compliant with the IEEE 802.3af Standard

Figure 4.

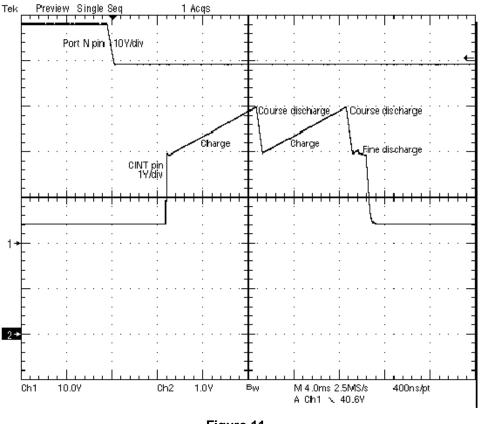

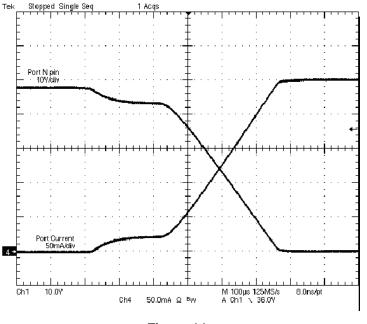

#### AM Power Delivery

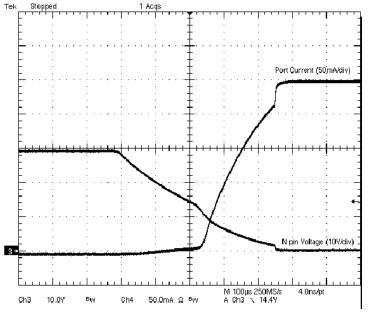

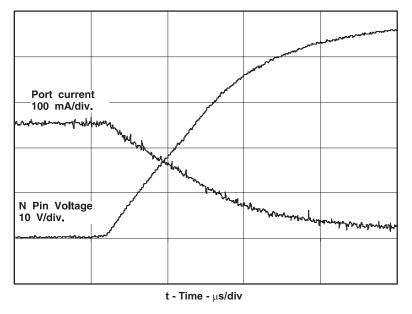

After successfully discovery and classification of a valid PD the power is delivered by controlling the current to the PD until its current requirements are met or until the internal current limit is reached (approximately 650 mA). The power switch is fully enhanced after 500  $\mu$ s. Figure 5 show the voltage and the current that is being applied to the PD during power-up and reaching the PD load of 250mA.

#### Figure 5.

After power has been applied to the PD the TPS23841 automatically enters the current and voltage sample mode. The sample mode performs 31 current measurements and 1 voltage measurement. Each measurement takes approximately 18 ms to complete. The port remains powered and the current/voltage measurement cycle continues until a fault condition occurs. The current and voltage measurements are both stored in the A/D current and voltage registers and can be accessed through the I<sup>2</sup>C pins. This allows power management in the A/M if it is desired.

### AM Faults and INTB Output

AM faults are:

- Port under and over voltage faults, (if enabled, see Over/Under Voltage Fault section)

- Over current faults

- Under current (DC Disconnect) fault

- Thermal shutdown (TSD) fault

- Watchdog timer faults (disabled via WD\_DIS pin)

Any one of the first four fault conditions listed above causes the port to shut down, and a 3-bit fault code to be latched into the affected port's Status Read 1 register (addr = 0100b). Watchdog faults cause all four ports to shut down. Faulted ports are temporarily disabled after a fault has been detected and latched.

The INTB pin is an open-drain, active-low output which is asserted if a fault condition occurs on any of the four ports. This indication is asserted for any of the port faults which result in a code displayed in the port status register (the faults listed in Table 8). In automode, the fault latch, the status register fault bits, and consequently, INTB assertion, are cleared by expiration of the 750-ms TED timer.

#### **Over/Under Voltage Fault**

For the TPS23841, port over and undervoltge detection is disabled by default after device POR. This continuous voltage monitoring feature can subsequently be enabled by writing a logic 1 to bit D2 in the Common Control register, assuming usage under the direction of a higher level controller, (i.e., usage in semi-auto mode).

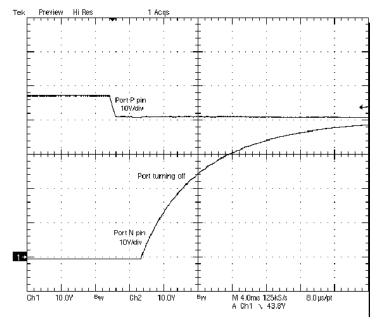

Over/under voltage faults are only processed after port power up has completed (voltage/power ramp to PD is done). The TPS23841 measures the voltage between the P and N pin and if this voltage drops below the under voltage threshold (typically 43 V) or increases above the over voltage threshold (typically 55 V) the voltage timer is turned on. When the voltage timer reaches its time-out limit that is set between 2 ms to 5 ms the corresponding port is turned off and the UV/OV fault code generated in the Port Status 1 register. If the over/under voltage condition is removed prior to the voltage timer reaching its limit the timer is reset and waits for the next event. Figure 6 shows a voltage fault lasting for more then 2 ms that has caused the port to shutdown.

Figure 6.

#### **Over Current or Current Limit Faults**

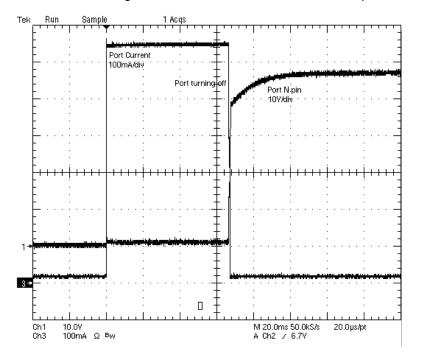

Over current or current limit faults are conditions when the load current that is being sensed trips either the  $I_{CUT}$  comparator (570 mA to 665 mA) or the  $I_{LIM}$  comparator (600 mA to 700 mA) and turns on the current fault timer. When the over current timer reaches its time out limit that is set between 50 ms to 75 ms the corresponding port is turned off and the over current fault code generated in the Port Status 1 register. If the over current condition goes away prior to the over current timer reaching its limit the timer is reset and waits for the next event. Figure 7 shows an over current fault lasting more than 50 ms that has caused the port to shut off.

Figure 7.

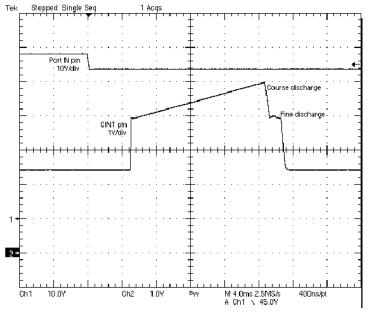

#### **Under Current Fault (DC Modulated Disconnect)**

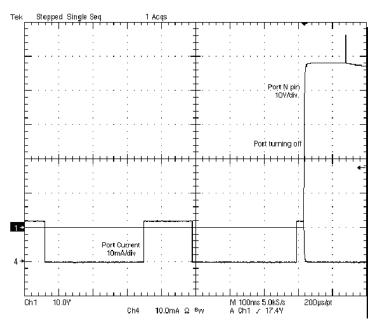

Under current fault (dc modulated disconnect) is a condition when the load current that is being measured drops below 7.5mA and turns on the disconnect timer. If the disconnect timer reaches its time out limit that is set between 300ms to 400ms the corresponding port is turned off and the load disconnect fault code generated in the Port Status 1 register. If the under current condition goes away prior to the disconnect timer reaching its limit the timer is reset and the port remains powered.

Figure 8 shows DC Disconnect event. In this setup the load current was set right above the 7.5mA threshold. The duty cycle of the load was then adjusted until the off period exceeded the disconnect time out, causing turn-off of the port. The time-out period was > 300 ms.

Figure 8.

### POWER MANAGEMENT MODE FUNCTIONAL DESCRIPTION

#### **Power Management Mode (PMM)**

Power management mode (PMM) has been designed to work efficiently with simple low-cost microcontrollers such as those in the MSP430 family.

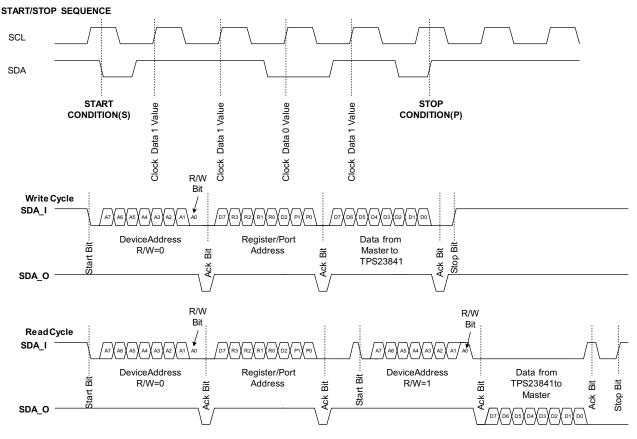

The power management mode uses 13 self-contained functions to completely control the device operation. You simply write/read through the l<sup>2</sup>C pins and wait for the function done bit to be set. If an A/D measurement was performed during the function the results can be accessed by going to the read mode and addressing the proper register.

#### **13 Funcitons**

- **Disable:** Disable the port and reset all functions.

- **Discovery 1:** Enable the Discovery 1 condition which applies a 4.4 V across the PD and measure and store the resulting current.

- **Discovery 2:** Enable the Discovery 2 condition which applies a 8.8 V across the PD and measure and store the resulting current.

- V Sample: Measure the voltage between the P and N pins and store the result in the A/D voltage register.

- Legacy: Enable the 3.5-mA current source formeasuring capacitance and measure the voltage across the P and N terminals and store the result in the A/D voltage register.

- Classify: Enable the classification condition which applies 17.7 V across the PD and measure and store the resulting current.

- **Rup Pwr:** Turn on the output switch while controlling the current being delivered to the PD until the PD current needs are met or the max current is reached.

- **C** Sample: Continuous cycle of 31 current measurements and 1 voltage measurement. After each measurement the contents of the appropriate register are updated.

- Rdwn: Turn off the output switch while controlling current until output current reaches 0 mA.

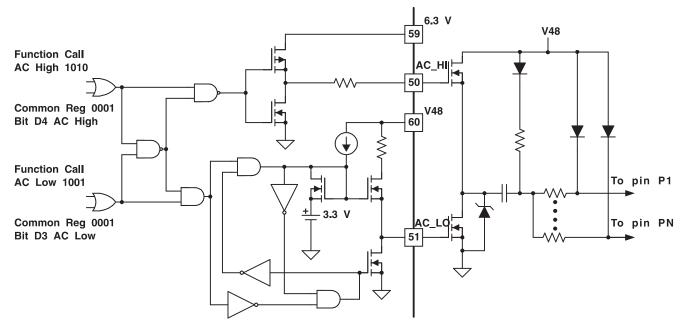

- AC LO: Turns on low side output FET and measures voltage between P and N pin and store result in A/D voltage registers.

- AC HI: Turns on high side output FET and measures voltage between P and N pin and store result in A/D voltage registers.

- **ISample:** Measure the current and store the result in the A/D current register.

- **TSample:** Measure the internal die temperature and store the result in the A/D temperature register.

Conversion times for A/D measurements performed as part of the functions listed above are generally as shown in the typical values in the Electrical Characteristics table. However, conversion time is somewhat dependant on the magnitude of the input signal being measured. Power management mode applications should take precautions to test the A/D DONE bit (MSB of the high byte) of the pertinent results register before accepting or using the returned value. A logic 1 at this bit location indicates the conversion is complete. Also, once an A/D conversion is in process on a given port, subsequent function calls to that port should wait until the currently executing conversion is complete. Commands written prior to completion may cause the results of the initial conversion to be written to the register of the subsequent function.

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | ╞→       | T Sample<br>1100   | Measure Die<br>Temperature<br>(18mS)            | Store Value                 | Set Done Bit                    | Waitfor Next<br>Function Call  |                                 |                                 |                                |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|--------------------|-------------------------------------------------|-----------------------------|---------------------------------|--------------------------------|---------------------------------|---------------------------------|--------------------------------|

| on is<br>4.4<br>ding                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | <b>→</b> | I Sample<br>1011   | Measure Chnl I<br>(18mS)                        | Set Done Bit                | Wait for Next<br>Function Call  |                                |                                 |                                 |                                |